Field Application Engineering Support

Summit’s Field Application Engineering department is available to answer technical questions and help customers implement good design for manufacturability practices. This team also provides feedback on PCB designs, drawings, stackups, and impedance.

Design for Manufacturing Reports

Summit has two types of DFM reports to help create a reliable and cost-effective design. These reports help eliminate potential holds and get PCBs in your hands without unnecessary delays.

DFM Check

This automated report is delivered in 1-2 days. It includes visuals and findings on design rules including:

- Minimum spacing violation

- Minimum width violation

- Annular ring violation

- Minimum PTH to copper violation

- Netlist validation

- and more.

Tooling DFM

This custom report includes visuals, detailed findings, and solutions. Typically delivered in 3-5 days, it gives you feedback on design specifications such as:

Board Outline Clearance

Board Thickness

Drill Diameter (Pad Diameter)

Drill to Copper Clearance

Conductor Width

Minimum Conductor Width

Clearance to Traces

Clearance to Pads

Clearance to Copper Fill

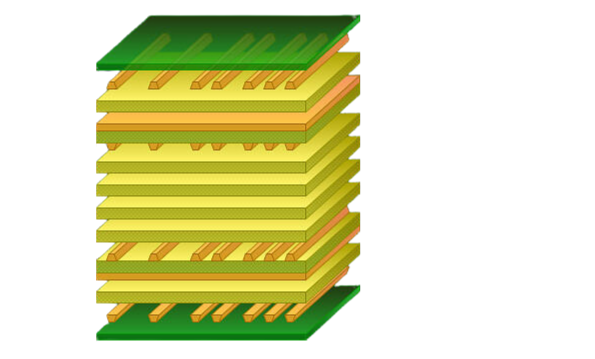

Stackup

We also provide preliminary stackup documents, which include:

- Stackup

- Impedance calculations

- Line width & spacing

- Copper weight and thickness

- Plated layers

- Dielectric thickness

- Layer types

- Materials

- Overall thickness

Contact Technical Support

Email Us

summit.fae@SummitInterconnect.comSend us an email

— Fill out the form below and send the message.

Additional technical resources

-

Article

09/02/20

Build a Better Via Stack

-

Article

06/09/20

Designing a Layer Stack

-

Video

04/03/20

DFM / DFA – What Is It? How Does It Work?

-

Article

07/27/22

IPC -2221B Section 10.1.4 Conductor Spacing

-

Article

09/22/22

IPC Rule for Land Sizes for a Plated Mechanically Drilled Hole

-

Article

03/27/21

IPC-4761 Via Protection Buried Vias Type V versus Type VII

-

Article

01/18/23

Let Me Vent!

Your connection to advanced PCB manufacturing

Your connection to advanced PCB manufacturing