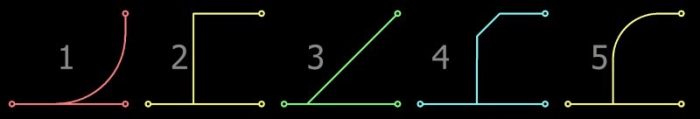

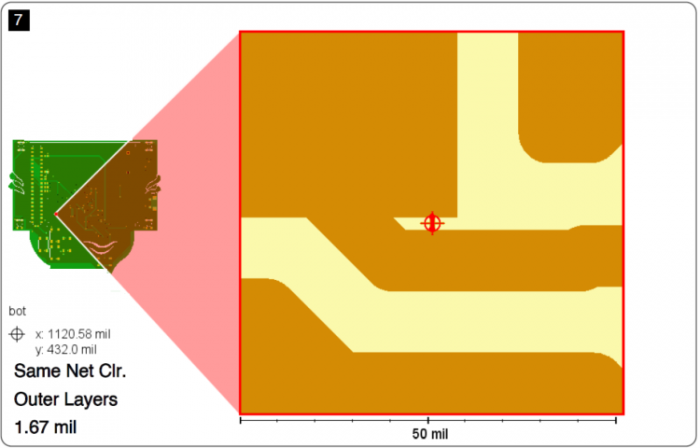

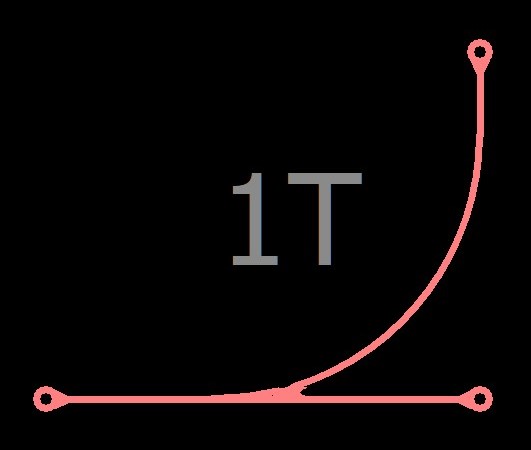

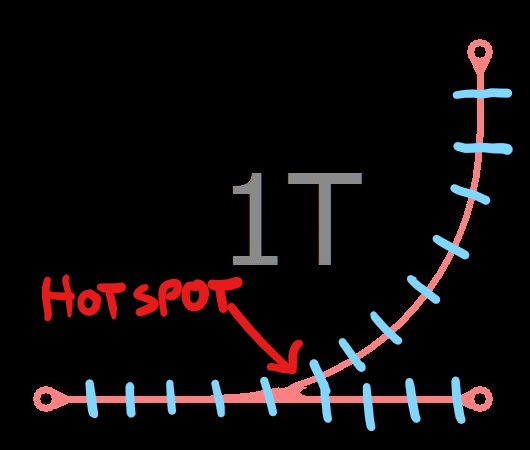

After part placement, the next step is to route traces between nets. An image below shows several examples of traces meeting at a t-intersection.

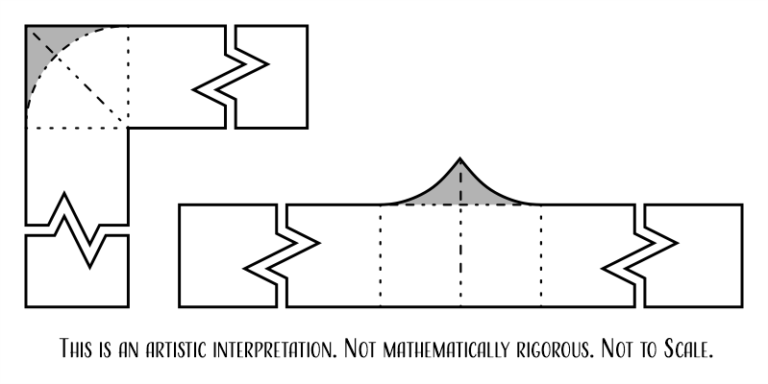

Acid Traps

If you talk to a collection of ten electrical engineers, nine of them will immediately discount options 1 and 3 due to the acute-angle intersections on the right side of where the traces meet. They will tell you that those angles create “acid-traps” — or locations where over-etching can occur. And while that might have still been a problem thirty years ago, fabrications processes have advanced to the state where it simply doesn’t matter anymore. You can draw a 1°-separation between traces on your fab designs if you wish. You won’t have issues with acid-traps, but you will have issues violating fabrication space-width minimums.

If you create a design that has a small angle in it, you fabricator might place a hold on your design. While they can easily close it by editing the gerber files, they have no way of knowing if your decision was an intentional feature to be kept or an oversight to be ignored. And they won’t make your board before checking with you first.

You can check for this problem by enabling “Same-net Clearance” checks while you perform your Design Rule Check in your EDA program.

High-Speed Reflections

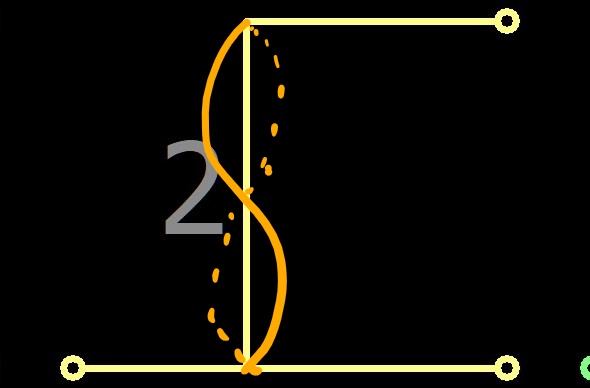

Engineers have a deep-seated hatred for right-angle turns, as shown in example 2 in image 1. A high-speed signal traveling along a trace will see an impedance discontinuity at a right-angle turn and another at the intersection.

Impedance discontinuities can cause reflections — if you have the right frequency and the right trace length, and a bit of bad luck, you can establish a standing wave in your trace. This has happened to electrical engineers, but it’s only a factor in extremely high-speed designs (>10 GHz) and unless your design requires non-fiberglass dielectrics, you don’t really need to worry about it.

The theoretical change in impedance at a right angle turn is 15%-20%. But the actual change in impedance is very difficult to measure.

But the theory doesn’t agree with empirical testing. Voltage transitions are not instantaneous — they occur over some amount of time and over some distance. Even a sub-nanosecond signal transition will occur over 100 – 500 mils distance. Most signal traces are less than ~10 mils wide, which places the discontinuity in that range as well. In short, the discontinuity is so short that it does not substantially affect the signal.

To visualize the discontinuity at a 90-degree bend requires high-end test equipment (oscilloscope with ps resolution and a time-domain reflectometer with ~30×10-12 s rise-time). Most logic-transitions are in the 10-9 or slower range. Therefore, the 90-degree bend simply doesn’t matter in practice.

You only need to worry about right-angles on very, very high-speed designs. There are other ESD and EMC concerns related to right-angles, but they aren’t usually a problem for new designers.

Thermal Dissipation

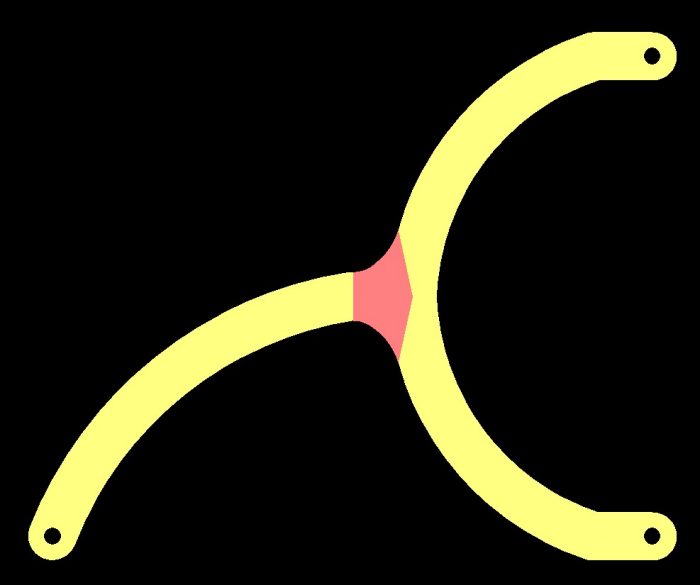

If you have a high-current trace, heat will dissipate outwards from the trace to cooler parts of the board. Usually, the thermal gradient is oriented perpendicular to the trace, outwards in both directions. But what if one of the areas the heat has to dissipate is shared by another part of the trace? Heat does not flow into hot locations — the thermal energy will remain in that section of the board, creating a hot-spot.

Best Option For Your Design

Use Image1, example 4 for your design: Curved traces often take more time to route and are overkill unless you want to use them for stylistic reasons.

Your connection to advanced PCB manufacturing

Your connection to advanced PCB manufacturing