# PCB 101 – How Boards are Manufactured

#### Presenter

#### **Laura Martin**

Director of Applications Engineering – Summit Interconnect

Laura Martin specializes in PCB Design for Manufacturing and works with customers to promote best design practices for manufacturability based on industry standards and Summit's technical capabilities.

Laura previously worked for Lockheed Martin for 15 years, initially in PCB manufacturing and then as leader of the producibility engineering department where she and her team reviewed all circuit board designs prior to release for manufacturing.

Email:

Laura.Martin@SummitInterconnect.com

Phone: (407) 212-8652

#### Overview

## Summit is the largest privately held PCB manufacturer in North America

- Eight North American-based facilities

- Multiple sites provide redundancy for customer risk mitigation

- Focused on providing the best customer experience with easy ordering and full transparency

- Broad range of PCB product capabilities

- Extensive quality certifications with continuous improvement processes

A total PCB solution from quick-turn prototype to volume production in a single manufacturing partner

#### A Complete Portfolio of PCB Products

#### Rigid

- High layer count

- Stacked microvias

- Complex miniature structures (i.e. blind/buried vias, via fill)

- Back drilling

- Multiple sequential lam

- Heat sinks

- Bonded, embedded coins

- Same-day turns available

#### Flex, Rigid-Flex

- Oversize, loose-leaf, bookbinder constructions

- Single-sided, double-sided, and multi-layer flex

- Adhesiveless and adhesive

- Stiffeners and connectors

- Laser ablation

- Thin flex laminates

- Flex assembly

#### RF / Microwave

- RF/digital hybrid designs

- Wide range of PTFE materials

- Mixed material stackups

- Plated cavities, edge plating

- Mode suppression/stitching

- Buried resistors

- Edge launch features

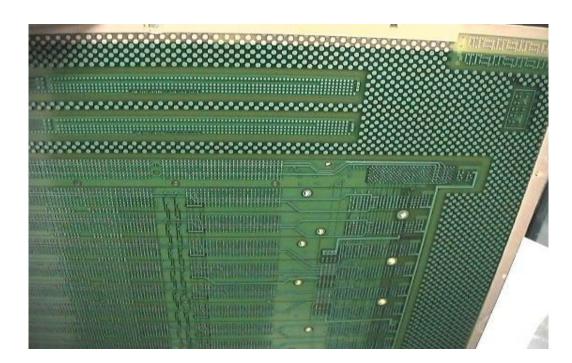

#### Semiconductor/ATE

- Reference, probe and load, and burn-in-boards

- High aspect ratio

- Low loss materials

- Bondable gold

- Tight tolerance drilling

- Ormet bonding

- Oversized panel options

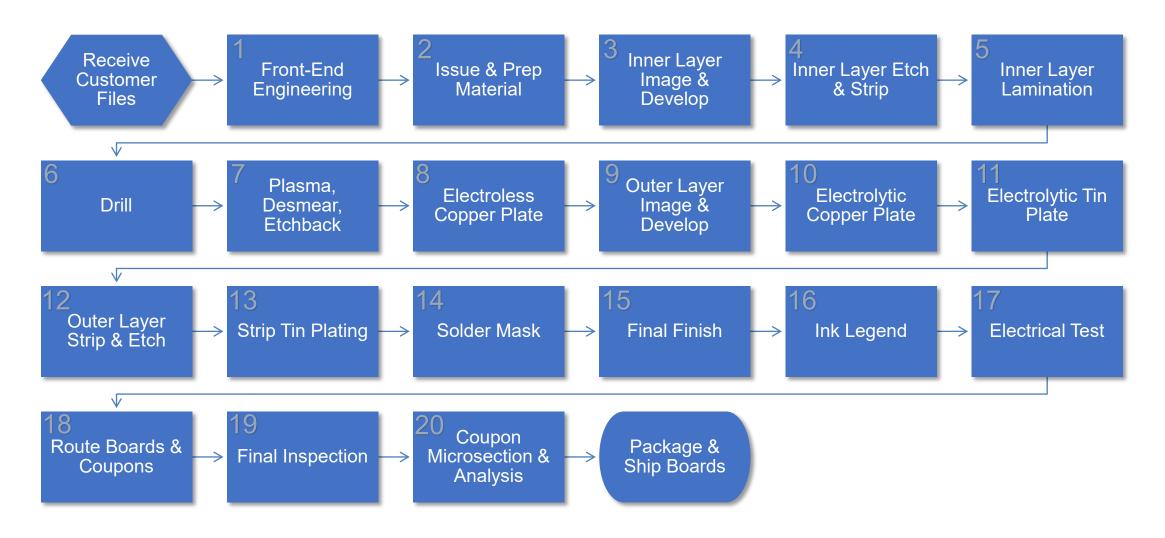

#### PCB Fabrication Process

## Step 1: Front-End Engineering

The process of **converting** customer **design** files to **working** data.

#### Planning Steps

- Review of all documentation

- Select material and panel size

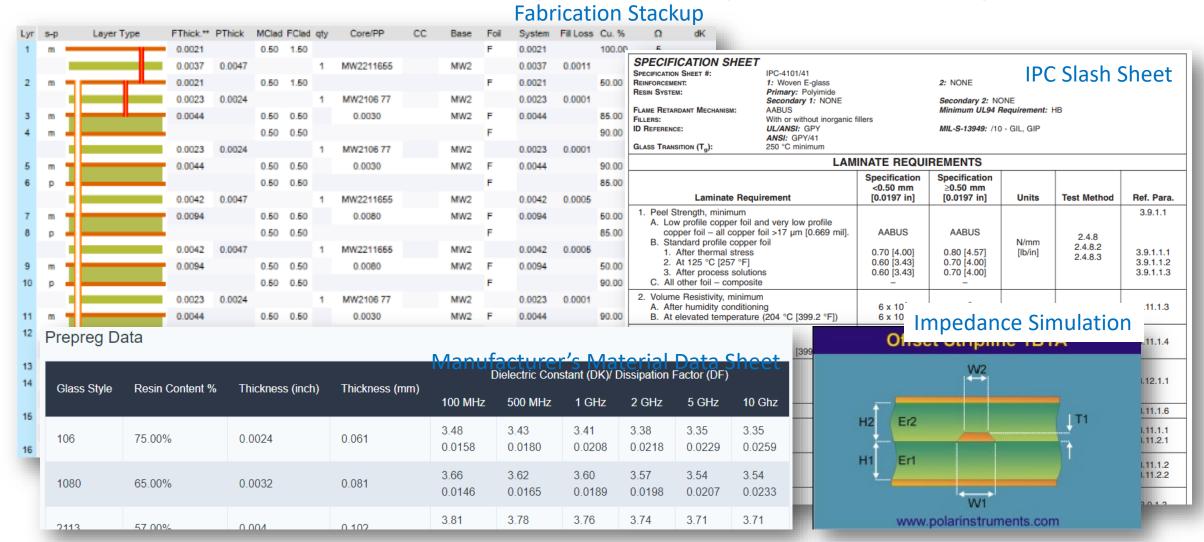

- Create material stack up and calculate impedance (if required)

- Create manufacturing travelers

- Release order to manufacturing floor

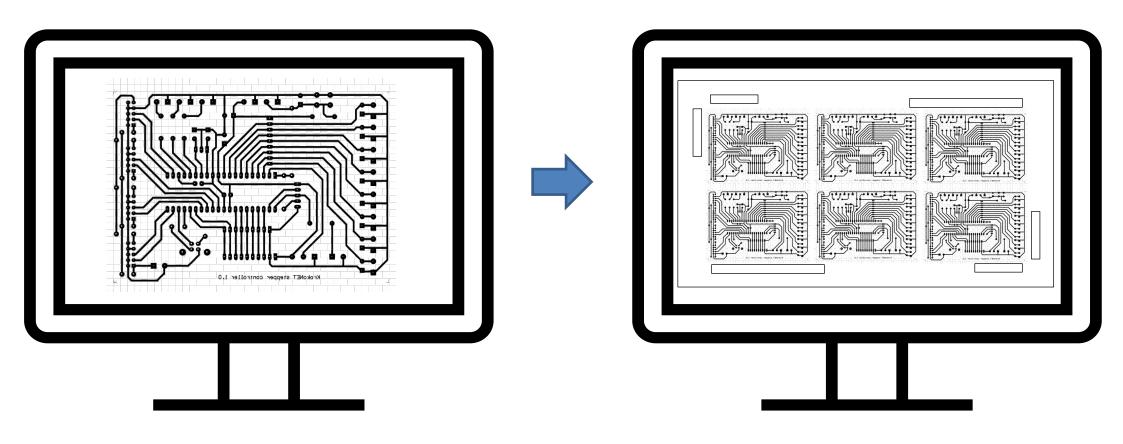

#### **CAM Steps**

- Import customer data

- Perform net compare & DFM checks

- Prepare data for manufacturing

- Panelize 1-up board

- Output files to production equipment

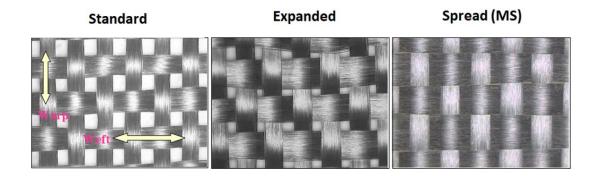

#### **Base Materials**

#### **Rigid Material**

IPC-4101 & IPC-4103

- Laminate Cores cured resin and glass fabric with copper on each side

- Prepreg Sheets uncured resin and glass fabric with no copper

- Different IPC slash sheets have different material properties

#### **Copper Foil**

IPC-4562

- Weight

- 1/4 oz, 3/8 oz, 1/2 oz, 1 oz, etc.

- Types

- Reverse Treated Foil (RTF)

- Very Low Profile (VLP)

- Rolled Annealed (RA)

- Etc.

## Step 1: Front-End Engineering - Planning

#### Step 1: Front-End Engineering - CAM

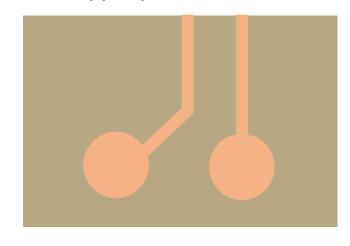

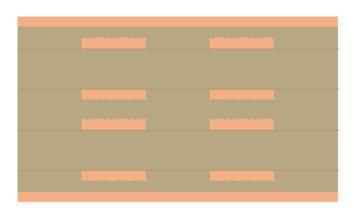

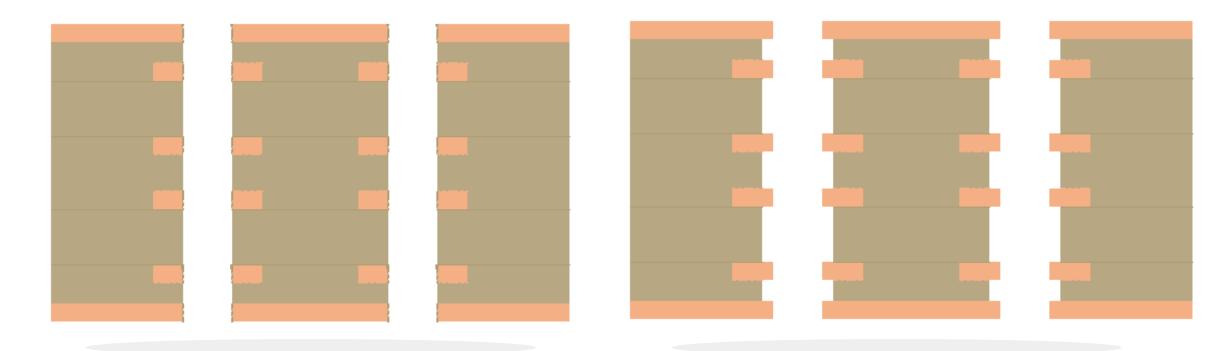

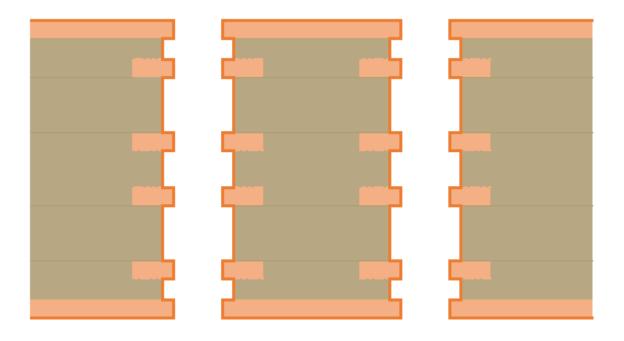

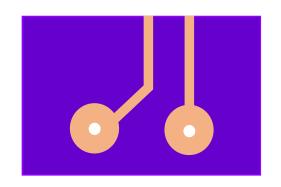

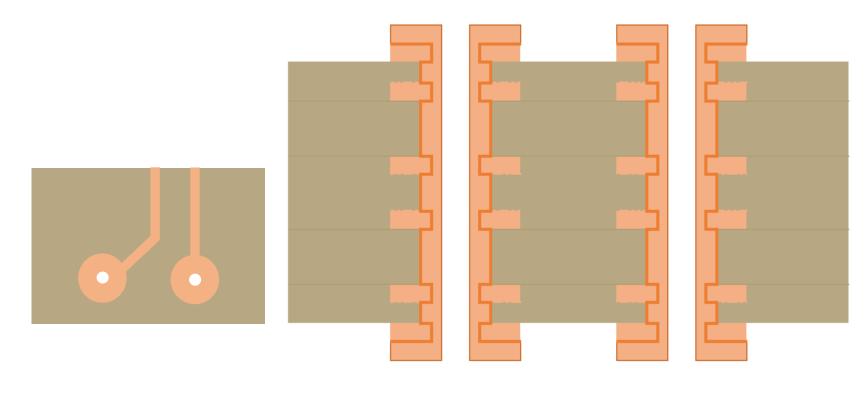

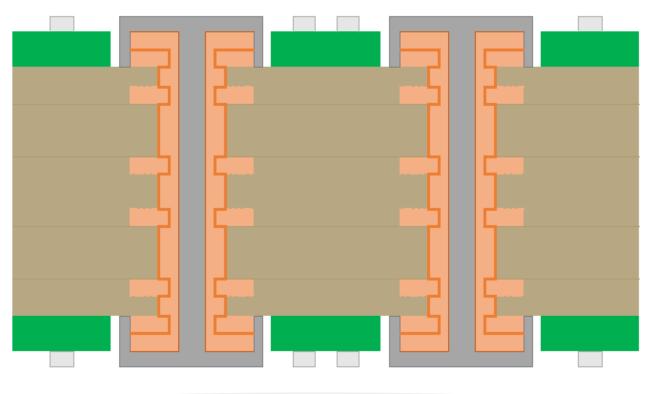

1-up board design

Multiple boards and test coupons placed in an array on selected panel size

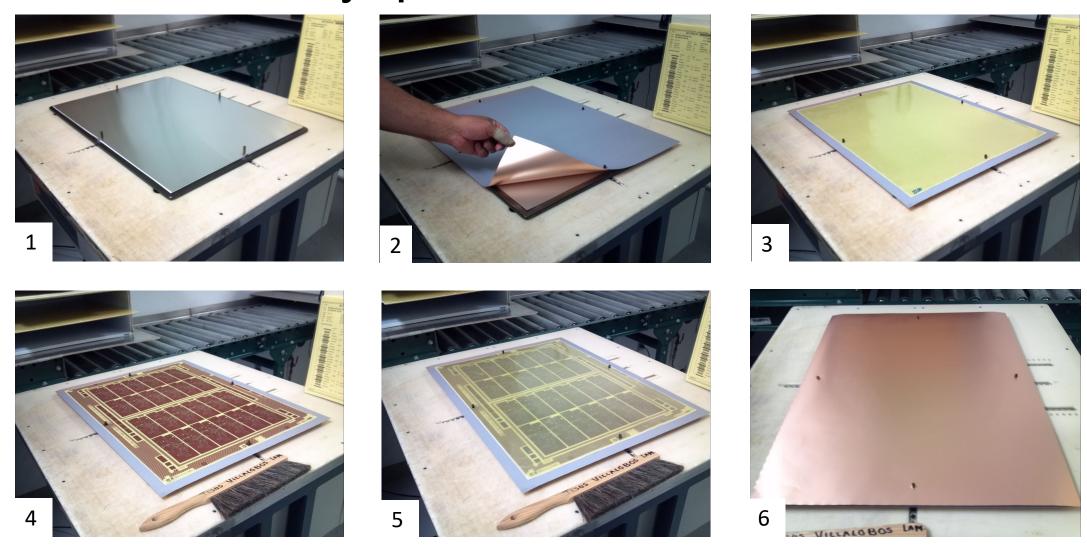

#### Step 2: Issue & Prep Material

- Core laminate is cleaned with an acid dip prior to photoresist process

- Prepreg sheets get tooled for lamination

Resin, glass, and copper substrate

a. Rigid core laminate

Substrate is coated with photo-imageable resist

b. Photoresist coat

## Step 3: Inner Layer Image & Develop

Circuit pattern is transferred to resist coated laminate by LDI

c. Image transfer

Pattern in resist is cured by the laser in previous step

d. Polymerized pattern in resist

Uncured resist is dissolved away

e. Circuit pattern in resist

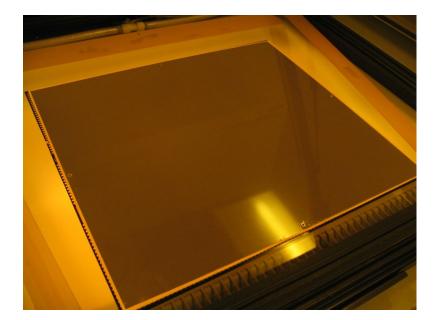

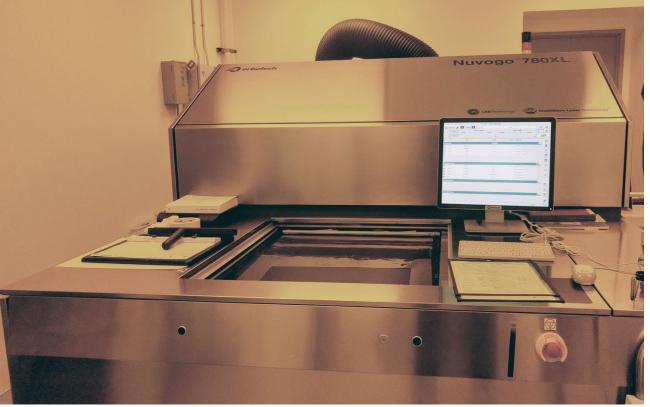

#### Laser Direct Image Equipment

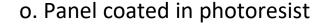

Inner layer coated with resist

Laser Direct Image Machine

Inner layer image transferred

## Step 4: Inner Layer Etch & Strip

Exposed copper is etched away down to the substrate

f. Etch copper

Resist is stripped and finished copper pattern remains

g. Final result

Finished layers then get post-etch punched in preparation for the next process: Inner Layer Lamination

#### **DES Line**

Develop, Etch, Strip (DES) Line

Completed inner layer

Post-etch punch

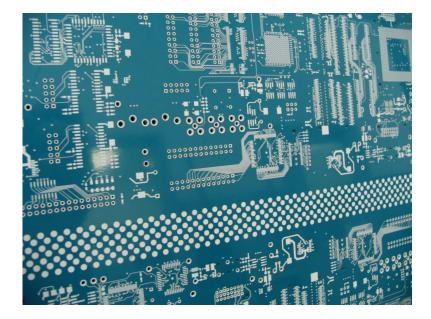

## **Automated Optical Inspection**

#### Step 5: Inner Layer Lamination

Copper is roughened (by oxide) to promote adhesion for lamination

h. Roughened copper

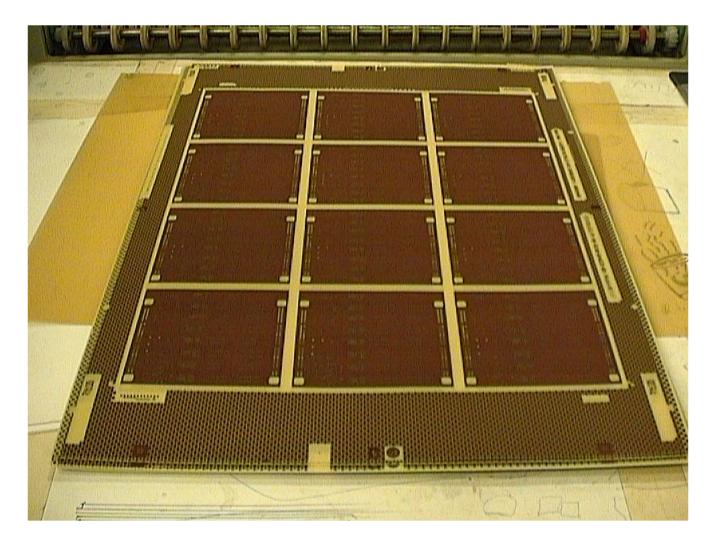

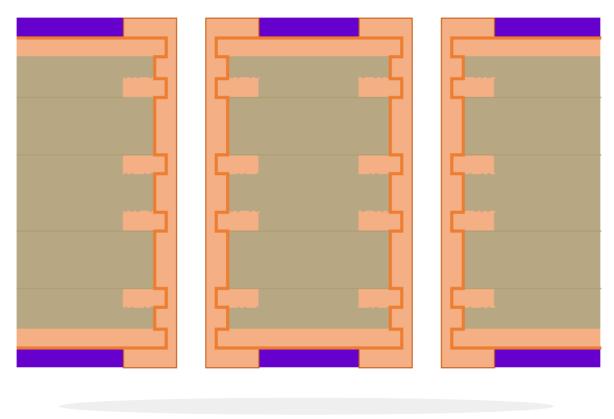

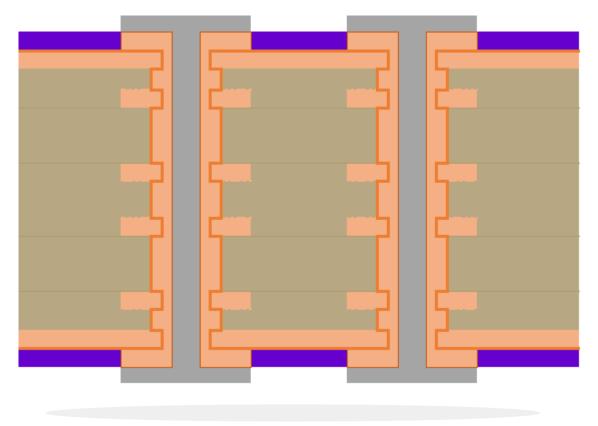

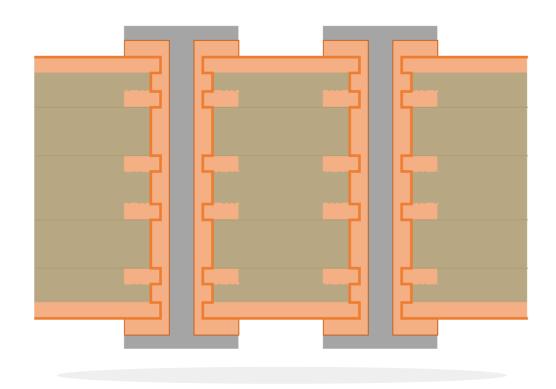

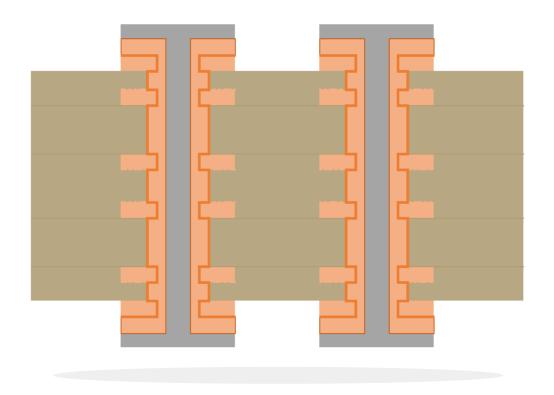

Laminate, prepreg, and outer copper layers are stacked up for lamination

Final result (often referred to as a sub or panel)

i. Materials stacked up

j. Laminated stackup

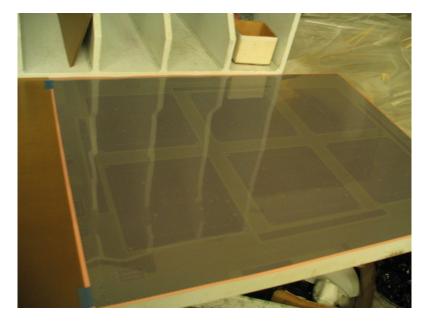

## Inner Layer Surface Oxide

## **Lamination Layup**

#### **Lamination Press Machine**

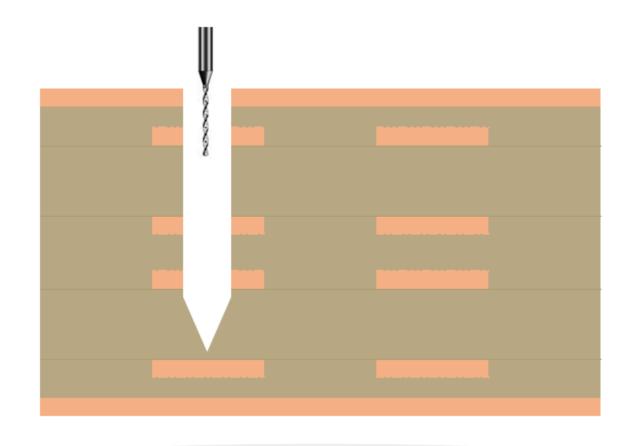

#### Step 6: Drill

- Prior to drilling, the panel is "flash routed" to remove resin squeeze-out from edges of panel

- An in-process coupon is "test" drilled and x-rayed to check registration prior to entire panel being drilled

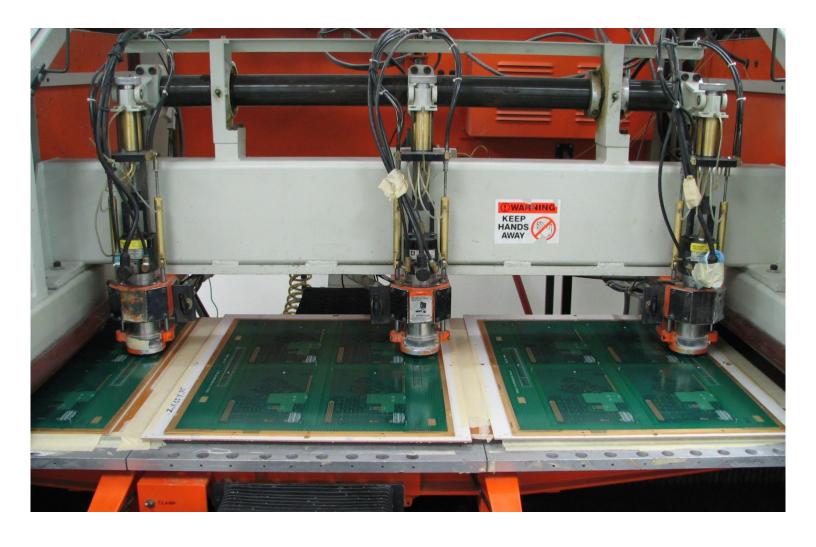

#### **Mechanical Drill**

#### Mechanical Drill

#### Step 7: Desmear, Plasma, Etchback

Drilled holes need to be prepared for electroless copper plating

A series of steps is performed to desmear and etch back copper

I. Resin smear in holes after drill process

m. Cleaned and prepped holes, and etchback

### Step 8: Electroless Copper Plate

- A conditioner charges side walls

- The palladium is attracted

- The reaction allows copper to start plating

Thin layer of electroless copper is chemically plated on non-conductive material

#### Hole Cleaning and Electroless Line

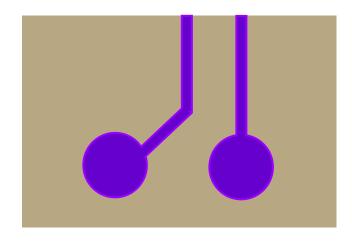

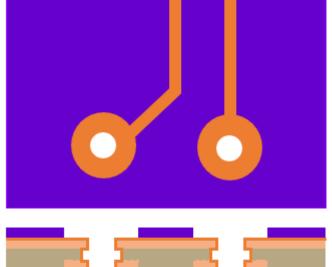

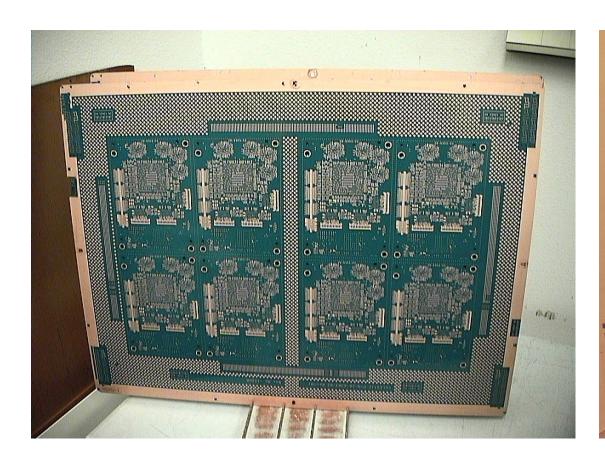

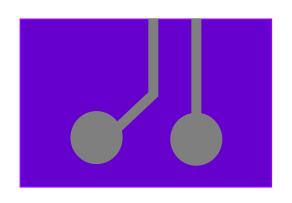

## Step 9: Outer Layer Image & Develop

- Same process as inner layers, except the reverse image is polymerized now

- Panel is coated with photoresist and outer layer image is transferred by LDI

- Resist dissolves over pattern to be plated

Inner layer image (negative)

Outer layer image (positive)

p. Outer layer image transferred

## Outer Layer Image

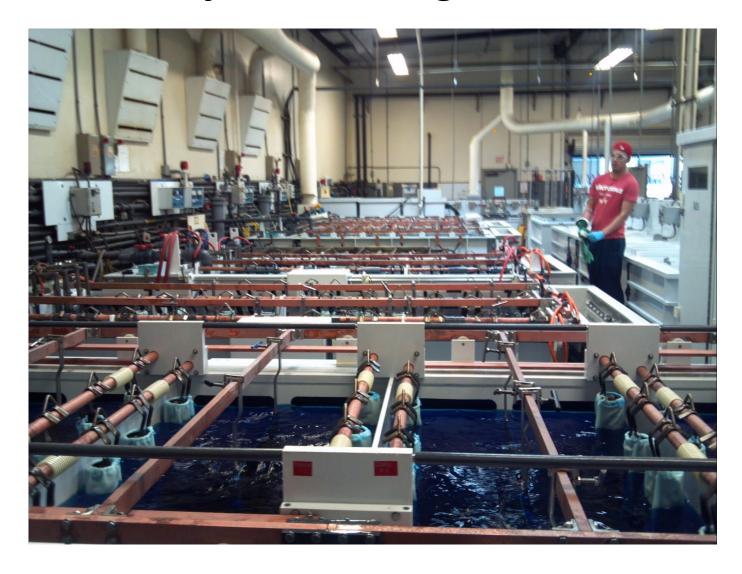

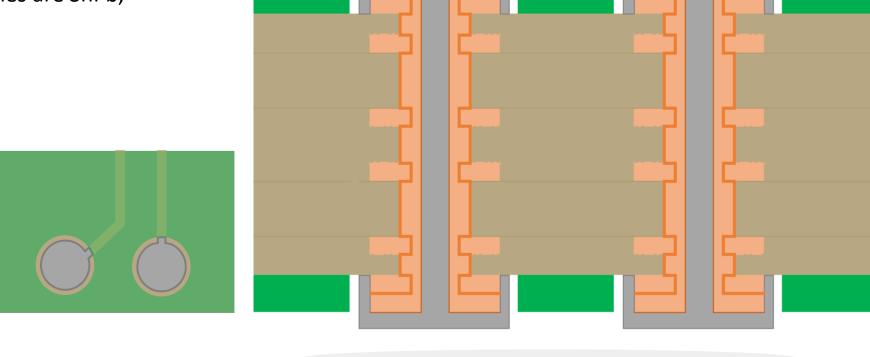

#### Step 10: Electrolytic Copper Plate

Electricity can now be used to plate surfaces made conductive from the electroless plating step

Copper is electrically plated until hole wall thickness requirements are met

q. Resist-free area is plated with electrolytic copper

## Electrolytic Plating Line

## Step 11: Electrolytic Tin Plate

Similar to photoresist, the plated tin protects the copper and can withstand the resist strip chemicals

Tin is plated over exposed copper and acts as a resist for the next process

r. Tin "resist" plating

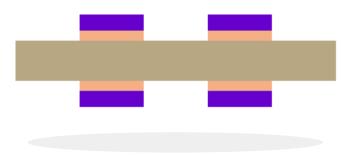

#### Step 12: Outer Layer Strip & Etch

The photoresist is stripped away, and remaining copper is exposed

Remaining exposed copper is etched away down to substrate

s. Stripped resist

t. Etched copper

## Tin Plate, Strip, and Etch

Tin plate with resist

Resist stripped

Etched copper

#### Step 13: Strip Tin Plating

Tin "resist" is stripped from panel, revealing final circuit pattern

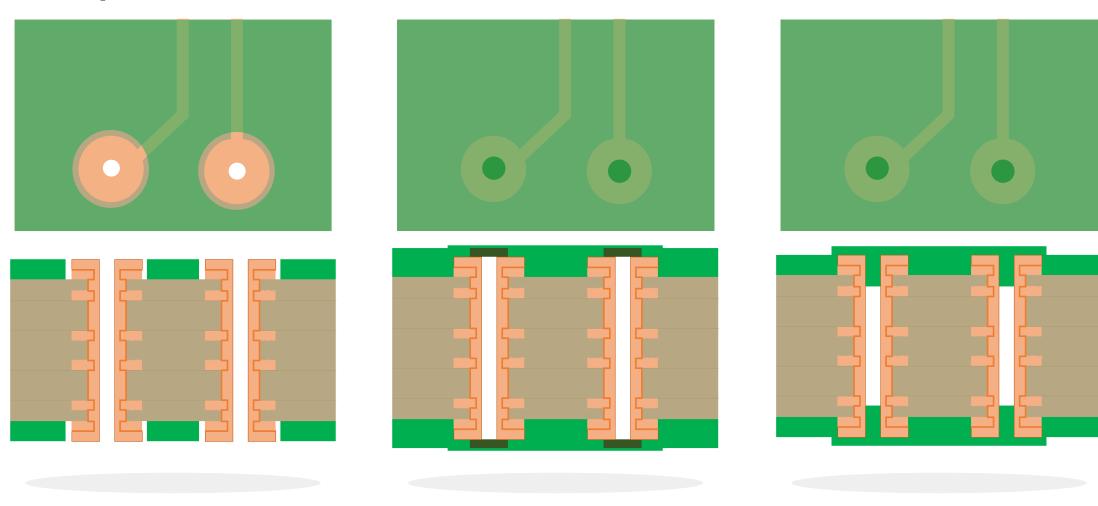

## Step 14: Solder Mask

a. Solder mask

b. Solder mask with dry film tent

c. Solder mask plugging

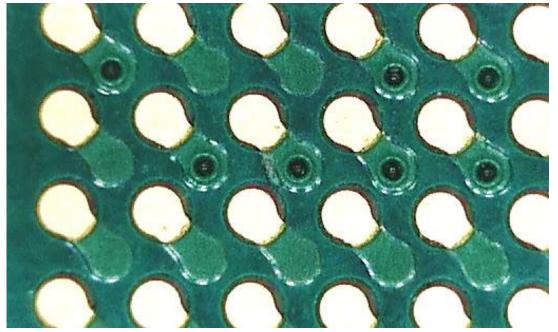

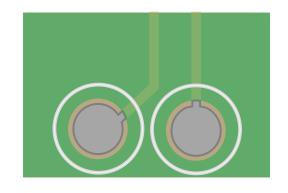

#### Solder Mask

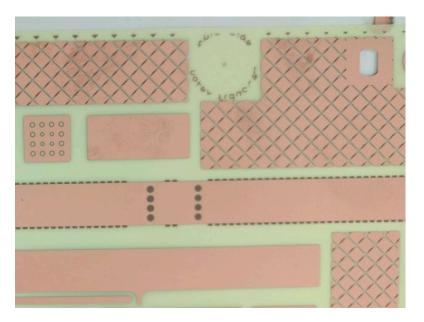

Panel coated with solder mask

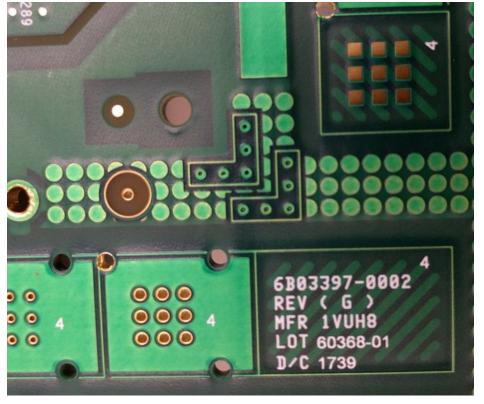

Close-up of exposed copper and covered vias

#### Step 15: Electrolytic Final Finish Plate

- Electroless Nickel, Immersion Gold (ENIG) is the most used final finish in North America

- Other common finishes are SnPb, HASL, ENEPIG, etc.

a. Final finish applied to exposed copper

#### Step 16: Ink Legend

The ink legend is often referred to as "silk screen" which is a term that originated from the prior way of "screening" legend onto boards

Legend is ink-jet printed over solder mask

a. Ink legend applied over solder mask

## Ink Legend Equipment

Ink Jet Printer

Legend

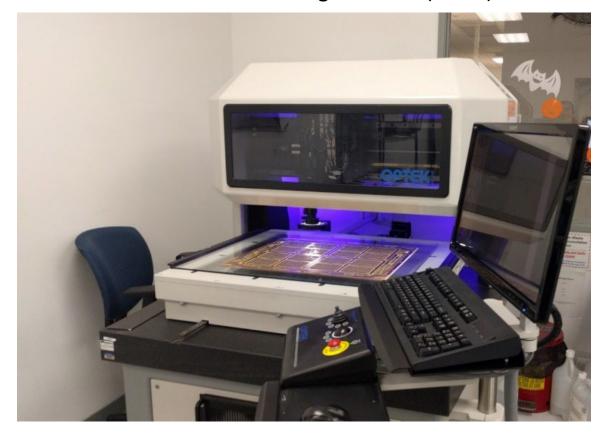

## Step 17: Electrical Test

#### Step 18: Route Boards & Coupons

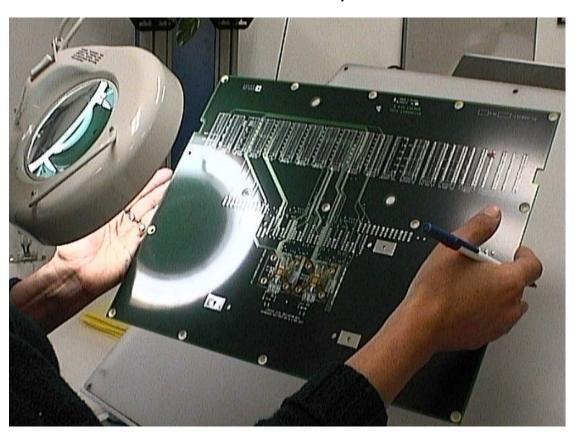

## Step 19: Final Inspection

**Final Inspection**

Coordinate Measuring Machine (CMM)

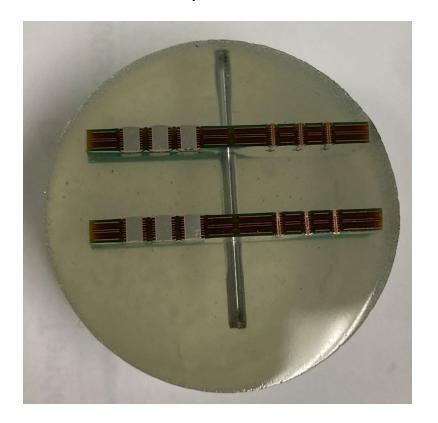

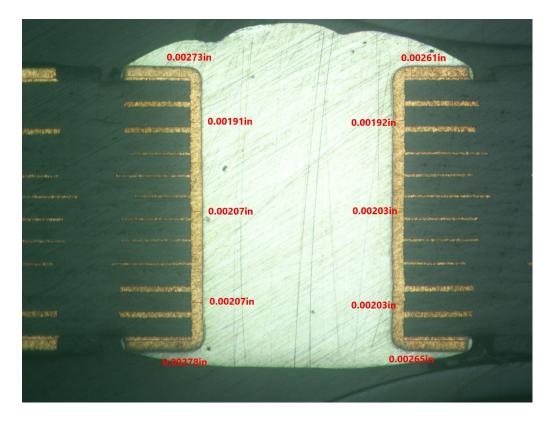

## Step 20: Coupon Microsection & Analysis

Coupon Puck

Cross-section of coupon

## Questions?